The output waveform \((Y)\) of the NAND gate for the following inputs \(A\) and \(B\) given in the figure is:

1.

2.

3.

4.

none of these

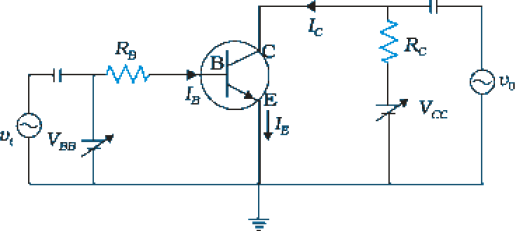

For a Silicon CE transistor amplifier, the audio signal voltage across the collector resistance of 2.0 k is 2.0 V. Suppose the current amplification factor of the transistor is 100, what should be the value of in series with the supply of 2.0 V if the dc base current has to be 10 times the signal current?

For a Silicon CE transistor amplifier, the audio signal voltage across the collector resistance of 2.0 k is 2.0 V. Suppose the current amplification factor of the transistor is 100 if the dc base current has to be 10 times the signal current. The dc current across through the collector resistance will be:

1. 0.1 mA

2. 10 mA

3. 1.0 mA

4. 0.01 mA

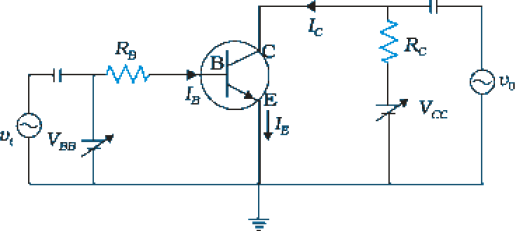

In figure, the supply can be varied from 0 V to 5.0 V. The Si transistor has = 250 and = 100 k, = 1 K, = 5.0 V. Assume that when the transistor is saturated, = 0 V and = 0.8V. The minimum base current, for which the transistor will reach saturation is:

In figure, the supply can be varied from 0 V to 5.0 V. The Si transistor has = 250 and = 100 k, = 1 K, = 5.0 V. Assume that when the transistor is saturated, = 0 V and = 0.8V. The input voltage for which the transistor will reach saturation is:

1. 0.8 V

2. 5.0 V

3. 2.8 V

4. 1.4 V

The electron concentration in an \(\mathrm{n\text-}\)type semiconductor is the same as the hole concentration in a \(\mathrm{p\text{-}}\)type semiconductor. An external field (electric) is applied across each of them. Compare the currents in them.

| 1. | current in \(\mathrm{n\text-}\)type \(>\) current in \(\mathrm{p\text{-}}\)type. |

| 2. | no current will flow in \(\mathrm{p\text{-}}\)type, current will only flow in \(\mathrm{n\text-}\)type. |

| 3. | current in \(\mathrm{n\text-}\)type \(=\) current in \(\mathrm{p\text{-}}\)type. |

| 4. | current in \(\mathrm{p\text{-}}\)type \(>\) current in \(\mathrm{n\text-}\)type. |

| Statement A: | A Zener diode is connected in reverse bias when used as a voltage regulator. |

| Statement B: | The potential barrier of \(\mathrm{p\text-n}\) junction lies between \(0.2\) V to \(0.3\) V. |

| 1. | Statement A is correct and Statement B is incorrect. |

| 2. | Statement A is incorrect and Statement B is correct. |

| 3. | Statement A and Statement B both are correct. |

| 4. | Statement A and Statement B both are incorrect. |

For the given circuit, the input digital signals are applied at the terminals \(A\), \(B\) and \(C\). What would be the output at terminal \(Y\)?

| 1. |  |

| 2. |  |

| 3. |  |

| 4. |  |

When a diode is forward biased, it has a voltage drop of 0.5 V. The safe limit of current through the diode is 10 mA. If a battery of emf 1.5 V is used in the circuit, the value of minimum resistance to be connected in series with the diode so that the current does not exceed the safe limit is-

1. 300

2. 50

3. 100

4. 200

The output waveform \((Y) \)of the AND gate for the following inputs \(A\) and \(B \) given in the figure, is:

| 1. |  |

| 2. |  |

| 3. |  |

| 4. | None of these |